Interrupts on the Nios II

Nios II uses non-vectored interrupts so all interrupts cause the program to

jump to the same fixed memory location, software at that location should

examine the control registers to determine which interrupts are active and

service one (or many) in some user-defined order. Below is a description of

the actions taken by the processor when an interrupt occurs, and similarly for

the eret instruction which is used to return from the interrupt. Also,

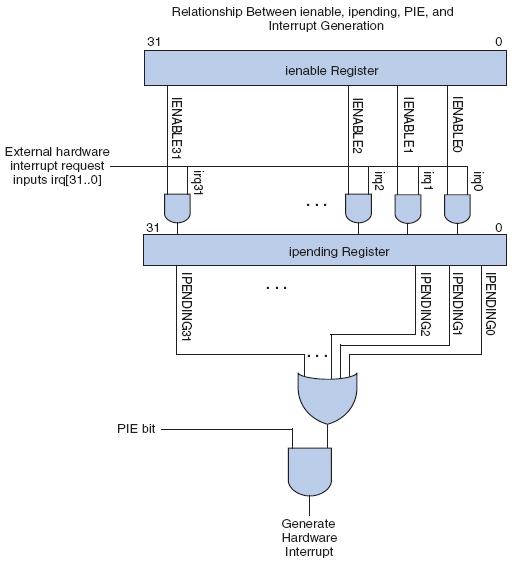

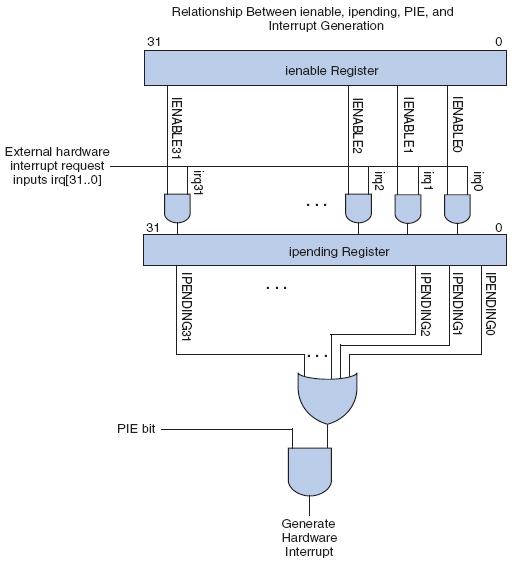

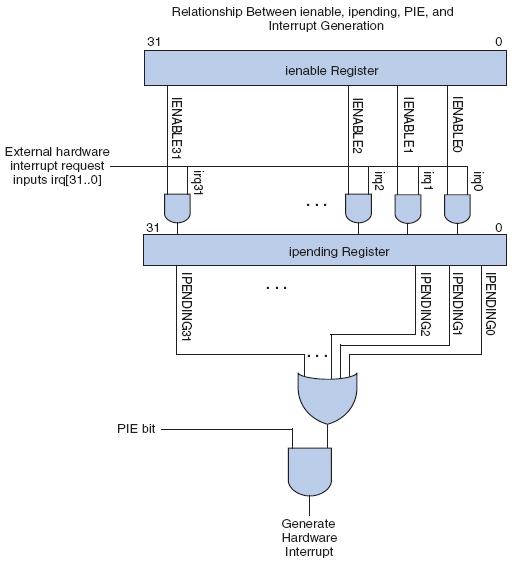

the Nios II interrupt hardware is shown in the figure below.

Anatomy of an Interrupt

The following actions are taken by the processor when an interrupt is triggered.

- The currently executing instruction is aborted

- The address of the next instruction after the exception is written to the ea register (r29). WARNING: You must decrement the ea register by 4 to execute the aborted instruction (unless that instruction caused the exception, such as an illegal instruction or the break instruction)

- The contents of the status register (ctl0) are copied to estatus (ctl1) saving the processor pre-exception status

- The PIE bit of the status register is cleared, disabling external processor interrupts

- The Program Counter is set to the address of the global exception handler

Anatomy of an Interrupt Return

The eret instruction is used to return from the exception handler. It performs the following actions.

- The ea register is copied into the Program Counter

- The estatus register is copied into the status register

Interrupt Hardware

The ienable(Ctl3) control register enables each IRQ line from 0-31. The

ipending(Ctl4) control register indicates which interrupts are being asserted.

If any interrupts are being asserted and the PIE bit in bit 0 of the

status control register is set, then an interrupt occurs.

Breakpoints Inside an Interrupt Service Routine

Note that the debugger has some quirks when debugging with code inside the

.exceptions section (so make sure only your ISR goes into .exceptions and the

rest of your code stays in .text).

Reference